將差分晶振PECL輸出連接到其他邏輯類型

來源:http://m.cbjur26.cn 作者:康華爾電子 2019年02月20

前面我們說到,LV-PECL和PECL實則屬于同一種差分輸出,還有一種CML輸出和EPCL差不多,那么要如何把PECL輸出連接到CML上呢,兩種相似的邏輯類型是否可以相融?為了驗證是否可靠,Pletronics晶振公司利用自家的LV9和PE9系列,做了以下實驗,請大家耐心閱讀。

除了LVPECL與LVPECL連接之外,還有可能將pletronics LVPECL振蕩器與其他邏輯系列一起使用,其中包括LVDS,CML和HSTL.Pletronics構成LVDS輸出晶振的復雜系列,因此通常不需要將LVPECL調整為LVDS nuless在非常高的頻率下要求。

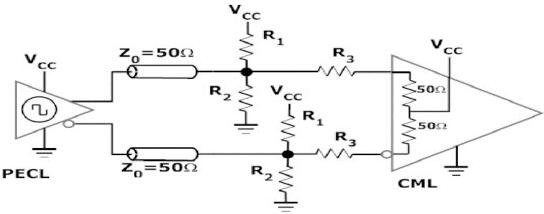

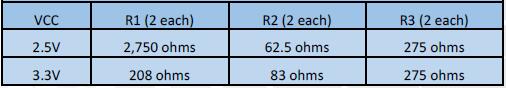

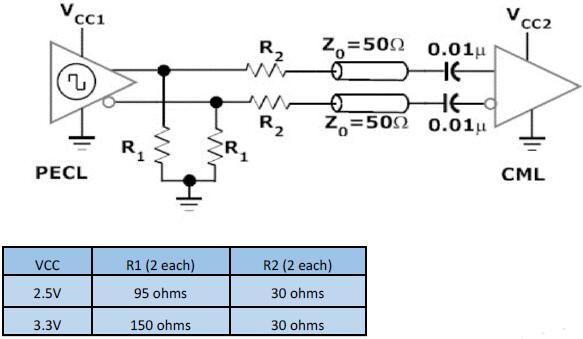

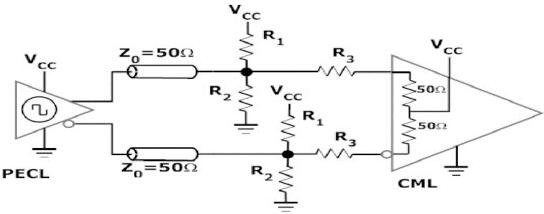

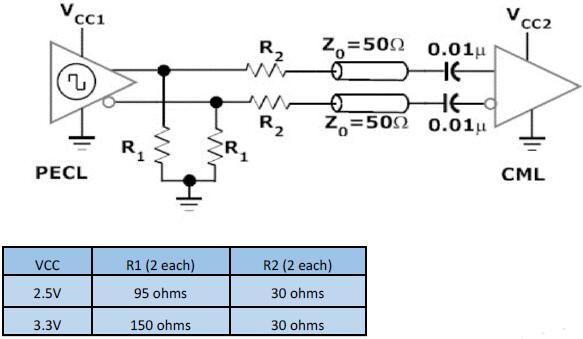

將PECL連接到CML:

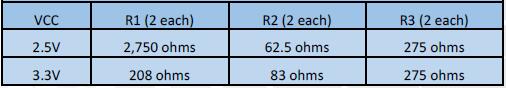

CML與ECL和PECL相似。但是,電壓擺幅和終端網絡存在差異.CML的差分電壓擺幅為400mv,LVPECL為800mv.CML輸入結構包括終端電阻,可能包括偏置電壓源,因此消除了對外部元件的需求。用于CML的偏置電壓不同于LVPECL,因此這也是一個考慮因素。

CML輸入的VCM和CML輸入上的信號擺動將需要使用允許的最小電平。CML輸入降至約0.125V PP,仍然在CML輸入最低級別規范內。因此R3為275歐姆。R1和R2的值的選擇與2.4節類似。在這種情況下,R1與串聯組合并聯R3和50歐姆CML終端。

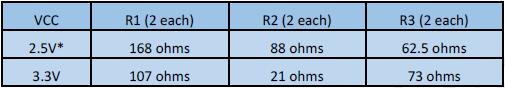

將PECL轉換為HSTL:

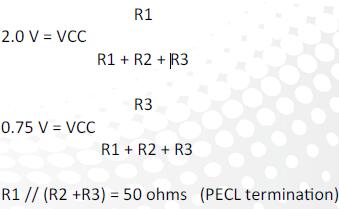

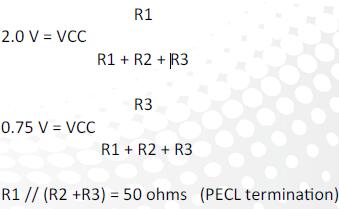

原理圖上的“a”點是PECL終端的VTT點(VCC-2.0V)。

原理圖上的“b”點是HSTL的Vref(0.75V)

.jpg)

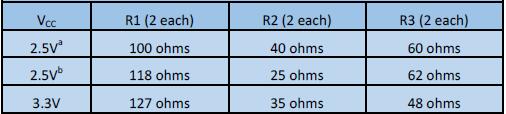

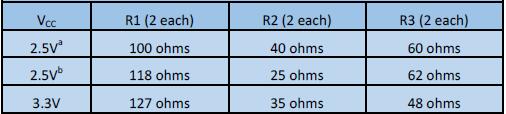

不幸的是,對于VCC=2.5V,沒有“完美”的解決方案。其中一個參數必須有折衷。有兩個好處。

'a'解決方案導致50歐姆PECL端接,HSTL VREF正確但PECL端接VTT只有1.25V。HSTL信號將是PECL信號的60%。

'b'解決方案導致50歐姆PECL端接,HSTL VREF正確,但PECL端接VTT只有1.44V。HSTL信號將是PECL信號的71%。

內部直流偏置時PECL與CML的接口

從LVPECL到CML的最廣泛使用的方法是通過AC耦合。交流耦合消除LVDS差分晶振和CML輸入級之間的任何共模電壓問題。在一些數據中應用中,基線漂移是AC耦合方案中的一個考慮因素,但這不是振蕩器的問題。在該方案中,兩個R1為振蕩器的射極跟隨器輸出級提供電流返回。對于CML兼容性,兩個R2將LVPECL輸出電壓擺幅降低約40%。

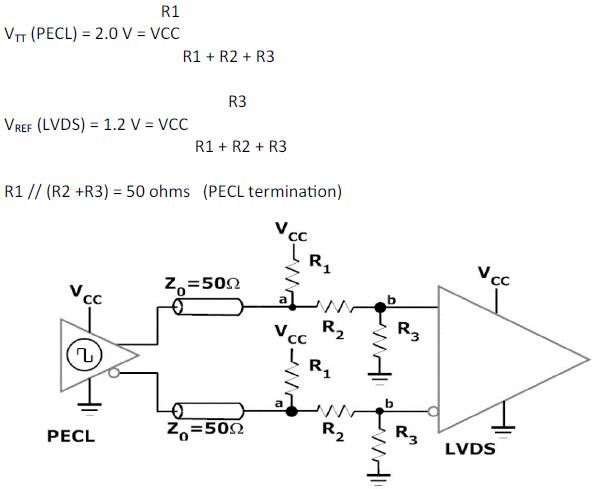

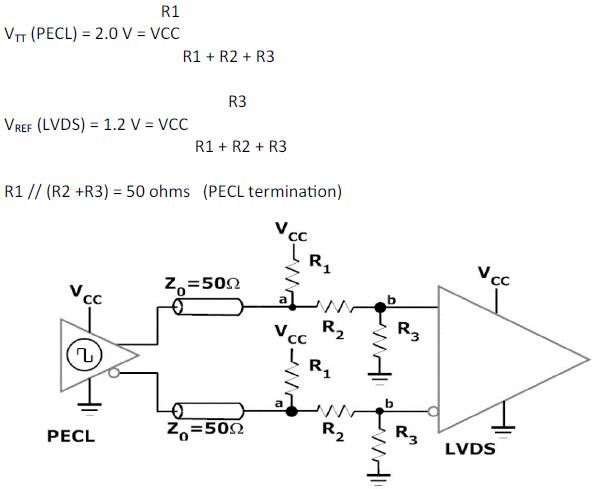

PECL與LVDS的接口將PECL衰減到LVDS電平:

Pletronics LV9差分晶體振蕩器系列LVDS輸出僅工作在700MHz。如果是更高頻率的LVDS信號需要時,這個PECL到LVDS接口提供了PE9系列上限的解決方案。

某些LVDS輸入無法接受過驅動。該解決方案將PECL峰峰值信號電平降低至LVDS電平和電平將信號轉換為LVDS 1.2V輸入平均電平。

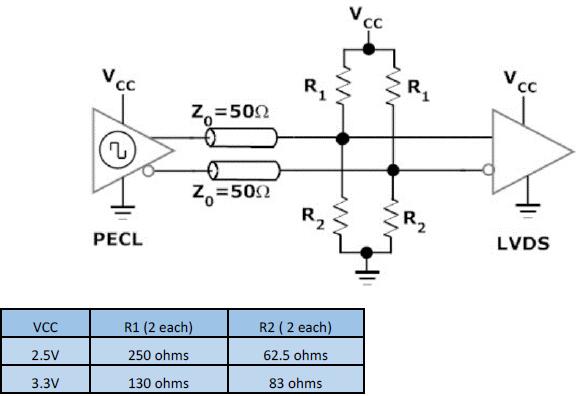

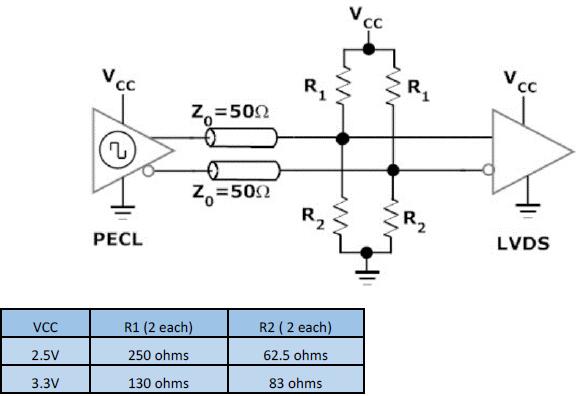

當LVDS可以接受更大的信號電平時:

將PECL連接到LVDS許多LVDS輸入將允許過驅動并具有寬共模范圍。在這種情況下,PECL電平可以直接驅動到LVDS輸入。這導致更簡單的電路。必須檢查LVDS輸入規范以確定此條件是否可接受。這也是假設LVDS差分晶振終端是外部的。

終端是標準PECL終端。

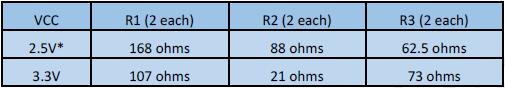

3.3V并沒有精確的解決方案,以下是最佳使用值:對于2.5V,原理圖必須更改,將R1從VCC移至'b'并將R3從'a'移至地。

注意:對于2.5V,原理圖已更改!

事實證明PECL輸出是可以連接到CML上的,至于其他的邏輯類型是否也一樣,還要留待后續的研究,為了讓工程師們更了解是如何操作,Pletronics Crystal公司畫出圖紙,制作表格和計算公式,懂的人也許一看就明了,外行人或者像我這樣一知半解的,估計都看懵了。差分晶體振蕩器如今已應用到更好的產品身上,使用數量和采購頻率也越來越多,前景還是相當不錯的,康華爾電子有正規渠道可幫客戶訂購國外進口品牌的差分晶振。

除了LVPECL與LVPECL連接之外,還有可能將pletronics LVPECL振蕩器與其他邏輯系列一起使用,其中包括LVDS,CML和HSTL.Pletronics構成LVDS輸出晶振的復雜系列,因此通常不需要將LVPECL調整為LVDS nuless在非常高的頻率下要求。

將PECL連接到CML:

CML與ECL和PECL相似。但是,電壓擺幅和終端網絡存在差異.CML的差分電壓擺幅為400mv,LVPECL為800mv.CML輸入結構包括終端電阻,可能包括偏置電壓源,因此消除了對外部元件的需求。用于CML的偏置電壓不同于LVPECL,因此這也是一個考慮因素。

CML輸入的VCM和CML輸入上的信號擺動將需要使用允許的最小電平。CML輸入降至約0.125V PP,仍然在CML輸入最低級別規范內。因此R3為275歐姆。R1和R2的值的選擇與2.4節類似。在這種情況下,R1與串聯組合并聯R3和50歐姆CML終端。

將PECL轉換為HSTL:

原理圖上的“a”點是PECL終端的VTT點(VCC-2.0V)。

原理圖上的“b”點是HSTL的Vref(0.75V)

.jpg)

不幸的是,對于VCC=2.5V,沒有“完美”的解決方案。其中一個參數必須有折衷。有兩個好處。

'a'解決方案導致50歐姆PECL端接,HSTL VREF正確但PECL端接VTT只有1.25V。HSTL信號將是PECL信號的60%。

'b'解決方案導致50歐姆PECL端接,HSTL VREF正確,但PECL端接VTT只有1.44V。HSTL信號將是PECL信號的71%。

內部直流偏置時PECL與CML的接口

從LVPECL到CML的最廣泛使用的方法是通過AC耦合。交流耦合消除LVDS差分晶振和CML輸入級之間的任何共模電壓問題。在一些數據中應用中,基線漂移是AC耦合方案中的一個考慮因素,但這不是振蕩器的問題。在該方案中,兩個R1為振蕩器的射極跟隨器輸出級提供電流返回。對于CML兼容性,兩個R2將LVPECL輸出電壓擺幅降低約40%。

PECL與LVDS的接口將PECL衰減到LVDS電平:

Pletronics LV9差分晶體振蕩器系列LVDS輸出僅工作在700MHz。如果是更高頻率的LVDS信號需要時,這個PECL到LVDS接口提供了PE9系列上限的解決方案。

某些LVDS輸入無法接受過驅動。該解決方案將PECL峰峰值信號電平降低至LVDS電平和電平將信號轉換為LVDS 1.2V輸入平均電平。

當LVDS可以接受更大的信號電平時:

將PECL連接到LVDS許多LVDS輸入將允許過驅動并具有寬共模范圍。在這種情況下,PECL電平可以直接驅動到LVDS輸入。這導致更簡單的電路。必須檢查LVDS輸入規范以確定此條件是否可接受。這也是假設LVDS差分晶振終端是外部的。

終端是標準PECL終端。

3.3V并沒有精確的解決方案,以下是最佳使用值:對于2.5V,原理圖必須更改,將R1從VCC移至'b'并將R3從'a'移至地。

注意:對于2.5V,原理圖已更改!

事實證明PECL輸出是可以連接到CML上的,至于其他的邏輯類型是否也一樣,還要留待后續的研究,為了讓工程師們更了解是如何操作,Pletronics Crystal公司畫出圖紙,制作表格和計算公式,懂的人也許一看就明了,外行人或者像我這樣一知半解的,估計都看懵了。差分晶體振蕩器如今已應用到更好的產品身上,使用數量和采購頻率也越來越多,前景還是相當不錯的,康華爾電子有正規渠道可幫客戶訂購國外進口品牌的差分晶振。

正在載入評論數據...

發表評論:

| 姓名: | |

| 郵箱: | |

| 正文: | |

歡迎參與討論,請在這里發表您的看法、交流您的觀點。

相關資訊

- [2024-02-18]CTS汽車級CA系列時鐘振蕩器

- [2024-01-20]TXC晶技5G通信專用小型7050mm恒...

- [2024-01-20]TXC恒溫晶體振蕩器新產品方案發...

- [2023-12-28]關于GEYER格耶品牌產品設計與支...

- [2023-12-28]GEYER格耶電子晶振公司的制品詳...

- [2023-11-06]Wi2Wi品牌發布其新的SN系列晶體...

- [2023-10-13]美國GED高質量時鐘晶體振蕩器

- [2023-09-25]H.ELE從原始石英晶體到精密晶體...

業務經理

業務經理